SI5330C-B00209-GMR vs P2I2305NZG-08SR

| Part Number |

|

|

| Category | Clock/Timing - Clock Buffers, Drivers | Clock/Timing - Clock Buffers, Drivers |

| Manufacturer | Skyworks Solutions Inc. | ON Semiconductor |

| Description | IC CLK BUFFER 1:4 HCSL 24QFN | IC CLK BUF 1:5 133.33MHZ 8SOIC |

| Package | Tape & Reel (TR) | Bulk |

| Series | - | - |

| Type | Fanout Buffer (Distribution), Translator | Fanout Buffer (Distribution) |

| Voltage - Supply | 1.71V ~ 3.63V | 3V ~ 3.6V |

| Operating Temperature | -40°C ~ 85°C | -40°C ~ 85°C |

| Mounting Type | Surface Mount | Surface Mount |

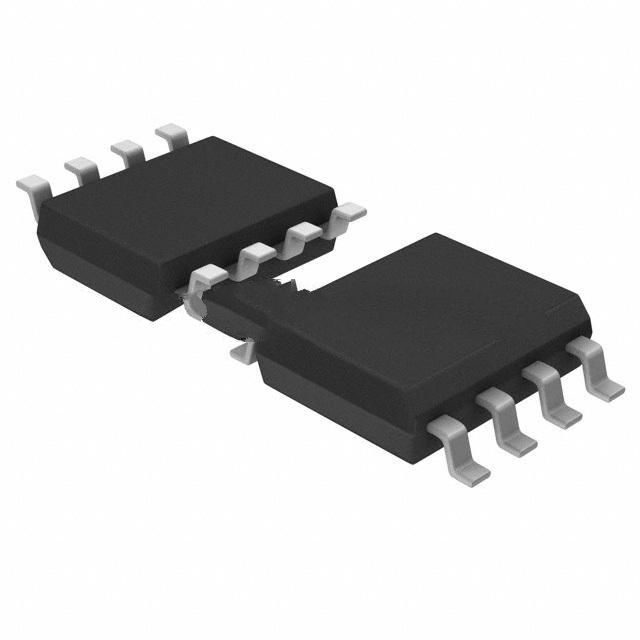

| Package / Case | 24-VFQFN Exposed Pad | 8-SOIC (0.154\", 3.90mm Width) |

| Supplier Device Package | 24-QFN (4x4) | 8-SOIC |

| Output | HCSL | CMOS |

| Frequency - Max | 250 MHz | 133.33 MHz |

| Number of Circuits | 1 | 1 |

| Input | CML, HCSL, LVDS, LVPECL | CMOS |

| Ratio - Input:Output | 1:4 | 1:5 |

| Differential - Input:Output | Yes/Yes | No/No |

-

1. What are the main applications of clock buffers?

Clock buffers are widely used in systems that require the distribution of clock signals to multiple devices, such as computer motherboards, servers, communication equipment, data centers, and industrial control systems, to ensure synchronized operation of all devices.

-

2. How to choose a suitable clock buffer?

When choosing a clock buffer, the following factors need to be considered:

frequency range

Number of output channels

Signal type (differential signal or single ended signal)

Phase noise and jitter performance

Power supply voltage and power consumption -

3. How to evaluate the performance of clock drivers?

When evaluating clock drivers, several key parameters need to be considered:

Driving capability (load capacity)

Output signal integrity

Phase noise and jitter

Power noise suppression

Power supply voltage range and power consumption

-

4. How do clock buffers and drivers help with timing design?

Clock buffers and drivers ensure that multiple components in the system can work synchronously at precise time points by providing stable, low jitter clock signals, thereby optimizing timing design, especially in high-performance computing and communication systems.