SL18861DI vs NB3L553MNR4G

| Part Number |

|

|

| Category | Clock/Timing - Clock Buffers, Drivers | Clock/Timing - Clock Buffers, Drivers |

| Manufacturer | Skyworks Solutions Inc. | ON Semiconductor |

| Description | IC CLK BUFFER 1:3 52MHZ 10TDFN | IC CLK BUFFER 1:4 200MHZ 8DFN |

| Package | Tape & Reel (TR) | Tape & Reel (TR) |

| Series | - | - |

| Type | Fanout Buffer (Distribution) | Fanout Buffer (Distribution) |

| Voltage - Supply | 1.7V ~ 3.65V | 2.375V ~ 5.25V |

| Operating Temperature | -40°C ~ 85°C | -40°C ~ 85°C |

| Mounting Type | Surface Mount | Surface Mount |

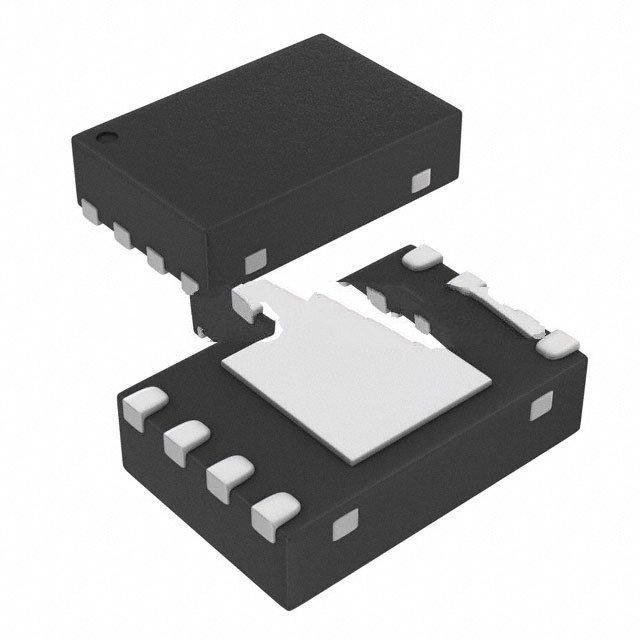

| Package / Case | 10-WFDFN | 8-VFDFN Exposed Pad |

| Supplier Device Package | 10-TDFN (2x1.4) | 8-DFN (2x2) |

| Output | LVCMOS | LVCMOS, LVTTL |

| Frequency - Max | 52 MHz | 200 MHz |

| Number of Circuits | 1 | 1 |

| Input | LVCMOS | LVCMOS, LVTTL |

| Ratio - Input:Output | 1:3 | 1:4 |

| Differential - Input:Output | No/No | No/No |

-

1. What is the function of a clock driver?

The function of a clock driver is to enhance the driving capability of the clock signal, ensuring that the signal can be transmitted further or drive more loads without causing signal attenuation or distortion. It is particularly important in high-frequency and high load applications.

-

2. How can clock buffers reduce jitter?

High quality clock buffers are typically designed with low jitter characteristics to ensure phase consistency of output signals and reduce phase noise during transmission. This is crucial for high-precision clock allocation, such as in communication and data transmission applications.

-

3. What output configurations does the clock buffer support?

Clock buffers typically support multiple output configurations, including single ended output, differential output, programmable delay, or selectable output frequency, to accommodate different system requirements.

-

4. How do clock buffers and drivers help with timing design?

Clock buffers and drivers ensure that multiple components in the system can work synchronously at precise time points by providing stable, low jitter clock signals, thereby optimizing timing design, especially in high-performance computing and communication systems.