Texas Instruments SN74ABTH16260DLR

- SN74ABTH16260DLR

- Texas Instruments

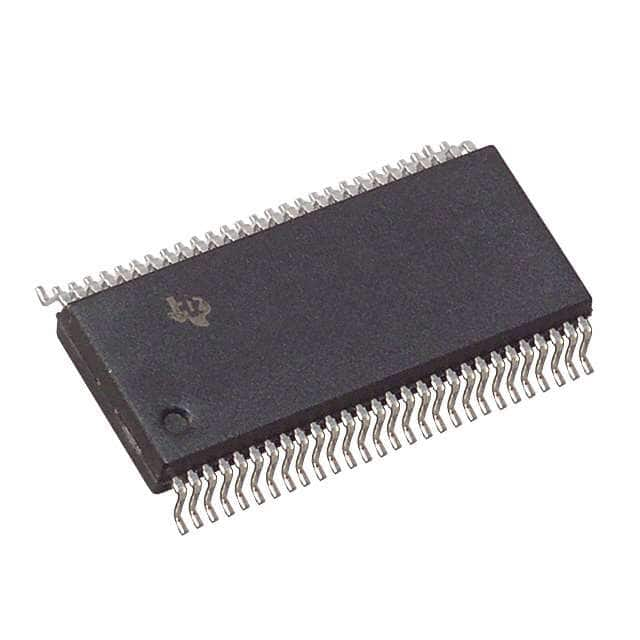

- IC 12-24 BIT MUX D LATCH 56-SSOP

- Logic - Latches

- SN74ABTH16260DLR Datasheet

- 56-BSSOP (0.295\", 7.50mm Width)

- Bulk

-

Lead free / RoHS Compliant

Lead free / RoHS Compliant - 26097

- Spot Inventory / Athorized Dstributor / Factory Excess Stock

- 1 year quality assurance 》

- Click to get rates

What is SN74ABTH16260DLR

Texas Instruments Part Number SN74ABTH16260DLR(Logic - Latches), developed and manufactured by Texas Instruments, distributed globally by Jinftry. We distribute various electronic components from world-renowned brands and provide one-stop services, making us a trusted global electronic component distributor.

SN74ABTH16260DLR is one of the part numbers distributed by Jinftry, and you can learn about its specifications/configurations, package/case, Datasheet, and other information here. Electronic components are affected by supply and demand, and prices fluctuate frequently. If you have a demand, please do not hesitate to send us an RFQ or email us immediately [email protected] Please inquire about the real-time unit price, Data Code, Lead time, payment terms, and any other information you would like to know. We will do our best to provide you with a quotation and reply as soon as possible.

SN74ABTH16260DLR Specifications

- Part NumberSN74ABTH16260DLR

- CategoryLogic - Latches

- ManufacturerTexas Instruments

- DescriptionIC 12-24 BIT MUX D LATCH 56-SSOP

- PackageBulk

- Series74ABTH

- Voltage - Supply4.5V ~ 5.5V

- Operating Temperature-40°C ~ 85°C

- Mounting TypeSurface Mount

- Package / Case56-BSSOP (0.295\", 7.50mm Width)

- Supplier Device Package56-SSOP

- Output TypeTri-State

- Circuit12:24

- Current - Output High, Low32mA, 64mA

- Logic TypeD-Type Transparent Latch

- Independent Circuits1

- Delay Time - Propagation3.2ns

Application of SN74ABTH16260DLR

SN74ABTH16260DLR Datasheet

SN74ABTH16260DLR Datasheet , Bulk,74ABTH,4.5V ~ 5.5V,-40°C ~ 85°C,Surface Mount,56-BSSOP (0.295\", 7.50mm Width),56-SSOP,Tri-State,12:24,32mA, 64mA,D-Type Transparent Latch,1,3.2ns

SN74ABTH16260DLR Classification

Logic - Latches

FAQ about Logic - Latches

-

1. What is latch logic?

A latch is a level-triggered storage unit that can keep its output state unchanged under certain conditions until a new input signal is received to change it.

Latches are usually used in combinational logic. When a signal needs to maintain its original value under certain conditions, the latch will be activated.

Working principle

The working principle of the latch is based on level triggering. When the latch is in the enabled state, its output will change with the change of the input signal; and when the latch is locked, the output will remain unchanged until the next enable signal arrives. The output state of the latch is determined by its input signal and the control signal.

Classification

There are many types of latches, the common ones are RS latches, gated RS latches and D latches. Taking the D latch as an example, its circuit is mainly composed of an RS latch composed of two NAND gates and a control circuit. The control signal is used to control whether the D input signal is latched.

-

2. What is the difference between NAND latches and NOR latches?

The main difference between NAND latch and NOR latch is their logic function and circuit structure.

Logic Function

NAND latch: When all inputs are high, the output is low; when at least one input is low, the output is high. This logic function makes the NAND latch output high as long as one of the multiple input signals is low.

NOR latch: When all inputs are low, the output is high; when at least one input is high, the output is low. This logic function means that the output will go low as long as one input is high. -

3. Why avoid using latches in FPGA?

The main reasons to avoid using latches in FPGA design include the following:

Circuit stability issues: Latches are sensitive to glitches and are easily disturbed by glitches on the signal, causing the circuit to become unstable.

Timing analysis difficulties: Latches are not conducive to static timing analysis because the timing characteristics of latches are unclear and the tool cannot determine the specific moment of data transmission, which may lead to timing violations and affect the performance and stability of the system.

Resource consumption issues: In FPGAs, the use of latches will lead to resource waste. For example, in Xilinx FPGAs, SLICEM resources can be configured as latches or flip-flops. If you choose to configure them as latches, the resources of other flip-flops will be wasted.

Debug and verification complexity: Designs containing latches will increase the complexity during debugging and verification because the behavior of latches is not as regular and predictable as registers.

Difficulty in optimization of synthesis tools: Modern synthesis tools are relatively mature and efficient in handling flip-flops, but the optimization of latches may not be ideal, which may lead to unsatisfactory results in terms of area and power consumption.

We are a professional PCB manufacturer who offers comprehensive PCB manufacturing services including: professional Ceramic PCB HDI PCB Heavy Copper PCB High-TG PCB High Speed PCB High Frequency PCB Metal Core PCB PCB fabrication and PCB assembly, providing fast turnaround prototypes for high-end products.

• Prompt Responsiveness

• Guaranteed Quality

• Global Access

• Competitive Market Price

• One-Stop support services of supply chain

Jinftry, Your most trustworthy component supplier, welcome to send us the inquiry, thank you!

Do you have any questions about SN74ABTH16260DLR ?

Feel free to contact us: